Önbellek hiyerarşisi - Cache hierarchy

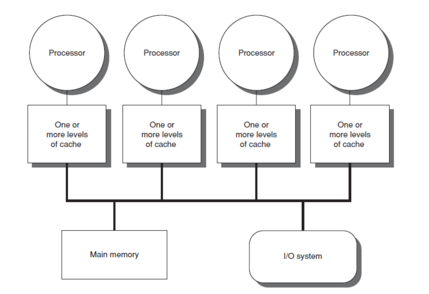

Önbellek hiyerarşisi, veya çok seviyeli önbellekler, verileri önbelleğe almak için değişen erişim hızlarına dayalı bir bellek deposu hiyerarşisi kullanan bir bellek mimarisini ifade eder. Çok talep edilen veriler, yüksek hızlı erişimli bellek depolarında önbelleğe alınır ve daha hızlı erişim sağlar. Merkezi işlem birimi (CPU) çekirdekler.

Önbellek hiyerarşisi bir biçim ve bir parçasıdır bellek hiyerarşisi ve bir biçim olarak düşünülebilir katmanlı depolama.[1] Bu tasarım, CPU çekirdeklerinin daha hızlı işlemesine izin vermek için tasarlandı. bellek gecikmesi nın-nin ana hafıza Giriş. Ana belleğe erişim, aşağıdakiler için bir darboğaz oluşturabilir: CPU çekirdek performansı CPU veri için beklerken, ana belleğin tamamını yüksek hızda yapmak çok pahalı olabilir. Yüksek hızlı önbellekler, CPU tarafından en çok kullanılan verilere yüksek hızlı erişim sağlayan bir uzlaşmadır ve daha hızlı CPU saati.[2]

Arka fon

Bilgisayar ve elektronik çip geliştirme tarihinde, CPU hızındaki artışların bellek erişim hızındaki iyileştirmeleri geride bıraktığı bir dönem vardı.[3] CPU'ların hızı ile bellek arasındaki boşluk, CPU'nun genellikle boşta olacağı anlamına geliyordu.[4] CPU'lar, belirli bir zamanda daha fazla miktarda talimat çalıştırma ve yürütme yeteneğine sahipti, ancak ana bellekten verilere erişmek için gereken süre, programların bu özellikten tam olarak yararlanmasını engelledi.[5] Bu sorun, daha hızlı işlemcilerin potansiyelini gerçekleştirmek için daha yüksek erişim oranlarına sahip bellek modellerinin oluşturulmasını motive etti.[6]

Bu kavramla sonuçlandı ön bellek, ilk öneren Maurice Wilkes, 1965'te Cambridge Üniversitesi'nde İngiliz bir bilgisayar bilimci. Bu tür bellek modellerine "köle bellek" adını verdi.[7] Yaklaşık 1970 ile 1990 arasında, makaleler ve makaleler Anant Agarwal, Alan Jay Smith, Mark D. Hill, Thomas R. Puzak ve diğerleri daha iyi önbellek tasarımlarını tartıştılar. İlk önbellek modelleri o sırada uygulandı, ancak araştırmacılar daha iyi tasarımlar araştırıp teklif ederken bile, daha hızlı bellek modellerine olan ihtiyaç devam etti. Bu ihtiyaç, ilk önbellek modellerinin maliyet ve teknik sınırlamalar açısından veri erişim gecikmesini iyileştirmesine rağmen, bir bilgisayar sisteminin önbelleğinin ana belleğin boyutuna yaklaşmasının mümkün olmadığı gerçeğinden kaynaklandı. 1990'dan itibaren, birinci seviye önbellek için bir yedek olarak başka bir önbellek seviyesi (ikinci seviye) eklemek gibi fikirler önerildi. Jean-Loup Baer, Wen-Hann Wang, Andrew W. Wilson ve diğerleri bu model üzerinde araştırma yaptılar. Birkaç simülasyon ve uygulama, iki seviyeli önbellek modellerinin avantajlarını gösterdiğinde, çok seviyeli önbellek kavramı yeni ve genellikle daha iyi bir önbellek bellek modeli olarak yakalandı. 2000 yılından bu yana, çok seviyeli önbellek modelleri geniş ilgi gördü ve şu anda Intel'in Core i7 ürünlerinde bulunan üç seviyeli önbellekler gibi birçok sistemde uygulanıyor.[8]

Çok seviyeli önbellek

Her bir komutun yürütülmesi için ana belleğe erişim, verilerin bulunması ve getirilmesi için gereken zamana bağlı olarak saat hızı ile yavaş işlemeye neden olabilir. Bu bellek gecikmesini işlemciden gizlemek için veri önbelleği kullanılır.[9] Veri işlemci tarafından ihtiyaç duyulduğunda, ana bellekten alınır ve önbellek adı verilen daha küçük bellek yapısında depolanır. Bu verilere daha fazla ihtiyaç duyulursa, ana belleğe gitmeden önce önbellek aranır.[10] Bu yapı, ana belleğe göre verileri aramak ve almak için geçen süre açısından işlemciye daha yakın bir yerde bulunur.[11] Önbellek kullanmanın avantajları, önbellekli ve önbelleksiz bellek hiyerarşisi için ortalama erişim süresi (AAT) hesaplanarak kanıtlanabilir.[12]

Ortalama erişim süresi (AAT)

Boyut olarak küçük olan önbellekler, sık sık yanlışlara neden olabilir - önbellekte yapılan bir arama aranan bilgiyi sağlamadığında - veri almak için ana belleğe bir çağrı ile sonuçlanır. Bu nedenle, AAT, verileri aradığı her yapının kayıp oranından etkilenir.[13]

Ana hafıza için AAT, Hit zamanı ile verilir ana hafıza. Önbellekler için AAT şu şekilde verilebilir:

- Vuruş zamanıönbellek + (Kaçırma oranıönbellek × Bayan Penaltıönbelleği kaybettikten sonra ana belleğe gitmek için geçen süre).[daha fazla açıklama gerekli ]

Önbelleklerin isabet süresi, ana belleğin isabet süresinden daha azdır, bu nedenle verilere ana bellek yerine önbellekten erişilirken veri alma için AAT önemli ölçüde daha düşüktür.[14]

Takas

Önbelleği kullanmak bellek gecikmesini iyileştirebilirken, önbelleklerin düzenlenme ve geçiş yapma şekli nedeniyle verileri almak için geçen süre için her zaman gerekli iyileştirmeyle sonuçlanmayabilir. Örneğin, aynı boyutta olan doğrudan eşlemeli önbelleklerin tam olarak ilişkilendirilen önbelleklerden genellikle daha yüksek bir hata oranı vardır. Bu aynı zamanda işlemciyi test eden bilgisayarın kıyaslamasına ve talimat modeline de bağlı olabilir. Ancak, tamamen ilişkilendirilebilir bir önbellek kullanmak, her seferinde tüm önbelleği aramak zorunda olduğu için daha fazla güç tüketimine neden olabilir. Bundan dolayı, güç tüketimi (ve ilgili ısı) ile önbelleğin boyutu arasındaki denge, önbellek tasarımında kritik hale gelir.[13]

Evrim

Önbellekte eksiklik olması durumunda, böyle bir yapının kullanım amacı işe yaramaz hale gelecek ve bilgisayarın gerekli verileri almak için ana belleğe gitmesi gerekecektir. Ancak, bir çok seviyeli önbellek, eğer bilgisayar işlemciye en yakın önbelleği (birinci düzey önbellek veya L1) kaçırırsa, sonraki en yakın önbellek (ler) i arar ve yalnızca bu yöntemler başarısız olursa ana belleğe gider. Genel eğilim, L1 önbelleğini küçük tutmak ve işlemciden 1-2 CPU saat döngüsü uzaklıkta tutmaktır; daha düşük önbellek seviyeleri, L1'den daha fazla veri depolamak için boyut olarak büyür, bu nedenle daha uzaktır, ancak daha az kaçırılır. oranı. Bu, daha iyi bir AAT ile sonuçlanır.[15] Önbellek düzeylerinin sayısı, maliyet, AAT'ler ve boyut arasındaki dengeler kontrol edildikten sonra, mimarlar tarafından gereksinimlerine göre tasarlanabilir.[16][17]

Performans kazanımları

Bellek sistemlerinin tek bir yonga üzerinde barındırılmasına izin veren teknoloji ölçeklendirmesiyle, günümüz işlemcilerinin çoğu üç veya dört önbellek seviyesine sahiptir.[18] AAT'deki azalma, bilgisayarın L3 önbelleklerine kadar farklı konfigürasyonlar için AAT'yi kontrol ettiği bu örnekle anlaşılabilir.

Misal: ana hafıza = 50ns, L1 =% 10 kayıp oranıyla 1 ns, L2 =% 1 kayıp oranıyla 5 ns), L3 =% 0,2 kayıp oranıyla 10 ns.

- Önbellek yok, AAT = 50 ns

- L1 önbellek, AAT = 1 ns + (0,1 × 50 ns) = 6 ns

- L1–2 önbellekleri, AAT = 1 ns + (0,1 × [5 ns + (0,01 × 50 ns)]) = 1,55 ns

- L1–3 önbellekleri, AAT = 1 ns + (0.1 × [5 ns + (0.01 × [10 ns + (0.002 × 50 ns)])]) = 1.5101 ns

Dezavantajları

- Önbellek hafızası artmış olarak geliyor marjinal maliyet ana bellekten daha fazla ve böylece genel sistemin maliyetini artırabilir.[19]

- Önbelleğe alınan veriler, yalnızca önbelleğe güç sağlandığı sürece saklanır.

- Bellek sistemi için artan yonga üzerinde alan.[20]

- Zayıf olan büyük bir program durumunda faydalar en aza indirilebilir veya ortadan kaldırılabilir. zamansal yerellik, ana belleğe sıklıkla erişen.[21]

Özellikleri

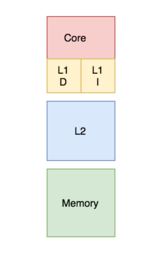

Bankalı ve birleştirilmiş

Bankalı bir önbellekte, önbellek, adanmış bir önbelleğe bölünmüştür. talimat depolama ve verilere ayrılmış bir önbellek. Buna karşılık, birleşik bir önbellek, aynı önbellekte hem talimatları hem de verileri içerir.[22] Bir işlem sırasında, hem talimatları hem de verileri almak için işlemci tarafından L1 önbelleğine (veya işlemciyle olan bağlantısıyla ilişkili olarak çoğu üst düzey önbelleğe) erişilir. Her iki eylemin de aynı anda uygulanmasını zorunlu kılmak, birden çok bağlantı noktası ve birleşik bir önbellekte daha fazla erişim süresi gerektirir. Birden fazla bağlantı noktasına sahip olmak, ek donanım ve kablolama gerektirir, bu da önbellekler ve işlem birimleri arasında önemli bir yapıya yol açar.[23] Bundan kaçınmak için, L1 önbelleği genellikle daha az bağlantı noktası, daha az donanım ve genellikle daha düşük erişim süreleri ile sonuçlanan bir yığılmış önbellek olarak düzenlenir.[13]

Modern işlemcilerin bölünmüş önbellekleri vardır ve çok düzeyli önbelleğe sahip sistemlerde, daha düşük düzeyler bölünürken daha yüksek düzey önbellekler birleştirilebilir.[24]

Dahil etme politikaları

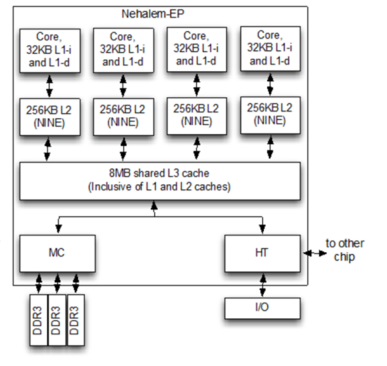

Üst önbellek katmanında bulunan bir bloğun alt önbellek düzeyinde de mevcut olup olmayacağı, bellek sisteminin dahil etme politikası tarafından yönetilir; bu, kapsayıcı, dışlayıcı veya kapsayıcı olmayan dışlayıcı (NINE) olabilir.[25]

Kapsayıcı bir politika ile, üst düzey önbellekte bulunan tüm bloklar, alt düzey önbellekte de bulunmalıdır. Her üst düzey önbellek bileşeni, alt düzey önbellek bileşeninin bir alt kümesidir. Bu durumda, blokların bir kopyası olduğu için, bir miktar bellek israfı vardır. Ancak kontrol daha hızlıdır.[25]

Özel bir politika kapsamında, tüm önbellek hiyerarşi bileşenleri tamamen özeldir, böylece üst düzey önbellekteki herhangi bir öğe, alt önbellek bileşenlerinin hiçbirinde bulunmayacaktır. Bu, önbelleğin tam olarak kullanılmasını sağlar. Ancak, yüksek bir bellek erişim gecikmesi vardır.[26]

Yukarıdaki politikalar, uygulanması için bir dizi kuralın izlenmesini gerektirir. Bunlardan hiçbiri zorunlu değilse, sonuçta ortaya çıkan dahil etme politikası, kapsayıcı olmayan münhasır olmayan (DOKUZ) olarak adlandırılır. Bu, üst düzey önbelleğin alt düzey önbellekte bulunabileceği veya bulunmayabileceği anlamına gelir.[21]

Politikaları yazın

Ana bellekte değiştirilmiş bir önbellek bloğunun güncellenme şeklini tanımlayan iki ilke vardır: yazma ve geri yazma.[25]

Yazma ilkesi durumunda, önbellek bloğunun değeri her değiştiğinde, alt düzey bellek hiyerarşisinde de değiştirilir.[27] Bu politika, verilerin hiyerarşi boyunca yazıldığı şekliyle güvenli bir şekilde saklanmasını sağlar.

Ancak, geri yazma ilkesi durumunda, değiştirilen önbellek bloğu, yalnızca önbellek bloğu kaldırıldığında daha düşük düzeydeki hiyerarşide güncellenecektir. Her önbellek bloğuna bir "kirli bit" eklenir ve önbellek bloğu her değiştirildiğinde ayarlanır.[28] Tahliye sırasında, ayarlanmış bir kirli bit bulunan bloklar, alt düzey hiyerarşiye yazılacaktır. Bu politika kapsamında, bir verinin en son değiştirilen kopyası yalnızca önbellekte saklandığından ve bu nedenle bazı düzeltici tekniklere uyulduğundan veri kaybı riski vardır.

Baytın önbellek bloğunda bulunmadığı bir yazma durumunda, bayt, bir yazma ayırma veya yazma tahsissiz ilkesi tarafından belirlendiği gibi önbelleğe getirilebilir.[25] Yazma ayırma ilkesi, bir yazma hatası durumunda bloğun ana bellekten getirildiğini ve yazmadan önce önbelleğe yerleştirildiğini belirtir.[29] Tahsisatsız yazma politikasında, önbellekte blok eksikse, bloğu önbelleğe getirmeden daha düşük seviyeli bellek hiyerarşisinde yazacaktır.[30]

Politikaların ortak kombinasyonları şunlardır: "blok yazma", "ayırma yazma" ve "ayırmadan yazma yoluyla yazma".

Bir işlemcideki belirli bir çekirdeğe özel bir önbellek atanır ve başka herhangi bir çekirdekten erişilemez. Bazı mimarilerde, her çekirdeğin kendi özel önbelleği vardır; bu, bir sistemin önbellek mimarisinde yinelenen blok riski yaratır ve bu da kapasite kullanımının azalmasına neden olur. Ancak, çok katmanlı bir önbellek mimarisindeki bu tür tasarım seçimi, daha düşük bir veri erişim gecikmesi için de iyi olabilir.[25][31][32]

Paylaşılan bir önbellek, birden çok çekirdek tarafından erişilebilen bir önbellektir.[33] Paylaşıldığı için, önbellekteki her blok benzersizdir ve bu nedenle yinelenen bloklar olmayacağından daha büyük bir isabet oranına sahiptir. Ancak, birden çok çekirdek aynı önbelleğe erişmeye çalıştıkça veri erişim gecikmesi artabilir.[34]

İçinde çok çekirdekli işlemciler, bir önbelleği paylaşma veya özel yapma tasarım seçimi işlemcinin performansını etkiler.[35] Uygulamada, üst düzey önbellek L1 (veya bazen L2)[36][37] özel olarak uygulanır ve alt düzey önbellekler paylaşımlı olarak uygulanır. Bu tasarım, yüksek seviyeli önbellekler için yüksek erişim oranları ve daha düşük seviyeli önbellekler için düşük kaçırma oranları sağlar.[35]

Son uygulama modelleri

Intel Broadwell mikromimarisi (2014)

- L1 önbelleği (talimat ve veriler) - 64kB çekirdek başına

- L2 önbellek - çekirdek başına 256 kB

- L3 önbellek - 2MB 6 MB paylaşıldı

- L4 önbellek - 128 MB eDRAM (yalnızca Iris Pro modelleri)[36]

Intel Kaby Lake mikro mimarisi (2016)

- L1 önbellek (talimat ve veri) - çekirdek başına 64 kB

- L2 önbellek - çekirdek başına 256 kB

- L3 önbellek - 2 MB - 8 MB paylaştırılmış[37]

AMD Zen mikro mimarisi (2017)

- L1 önbellek - 32 kB veri ve çekirdek başına 64 kB talimat, 4 yollu

- L2 önbellek - çekirdek başına 512 kB, 4 yollu dahil

- L3 önbellek - 4 çekirdekli CCX başına 4 MB yerel ve uzak, yonga başına 2 CCX, 16 yollu dahil değildir. Masaüstü CPU'larında 16 MB'a ve sunucu CPU'larında 64 MB'a kadar

AMD Zen 2 mikromimarisi (2019)

- L1 önbellek - 32 kB veri ve çekirdek başına 32 kB talimat, 8 yollu

- L2 önbellek - çekirdek başına 512 kB, 8 yollu dahil

- L3 önbellek - 4 çekirdekli CCX başına 16 MB yerel, yonga başına 2 CCX, 16 yol dahil değildir. Masaüstü CPU'larında 64 MB'a ve sunucu CPU'larında 256 MB'a kadar

IBM Power 7

- L1 önbellek (talimat ve veri) - her biri 64-bankalı, her bankanın 2rd + 1wr portu 32 kB, 8 yollu ilişkilendirilebilir, 128B blok, üzerinden yazma

- L2 önbellek - 256 kB, 8 yollu, 128B blok, geri yazma, L1 dahil, 2 ns erişim gecikmesi

- L3 önbellek - 4 MB'lik 8 bölge (toplam 32 MB), yerel bölge 6 ns, uzak 30 ns, her bölge 8 yollu ilişkilendirilebilir, DRAM veri dizisi, SRAM etiket dizisi[39]

Ayrıca bakınız

- Güç7

- Intel Broadwell Mikromimarisi

- Intel Kaby Lake Mikromimarisi

- CPU Önbelleği

- Bellek hiyerarşisi

- CAS gecikmesi

- Önbellek (bilgi işlem)

Referanslar

- ^ Hennessy, John L; Patterson, David A; Asanović, Krste; Bakos, Jason D; Colwell, Robert P; Bhattacharjee, Abhishek; Conte, Thomas M; Duato, José; Franklin, Diana; Goldberg, David; Jouppi, Norman P; Li, Sheng; Muralimanohar, Naveen; Peterson, Gregory D; Pinkston, Timothy Mark; Ranganathan, Prakash; Wood, David Allen; Young, Clifford; Zeky, Amr (2011). Bilgisayar Mimarisi: Nicel Bir Yaklaşım (Altıncı baskı). ISBN 978-0128119051. OCLC 983459758.

- ^ "Önbellek: Neden Düzleştirilsin" (PDF).

- ^ Ronald D. Miller; Lars I. Eriksson; Lee A Fleisher, 2014. Miller's Anesthesia E-Book. Elsevier Sağlık Bilimleri. s. 75. ISBN 978-0-323-28011-2.

- ^ Albert Y. Zomaya, 2006. Doğadan İlham Alan ve Yenilikçi Hesaplama El Kitabı: Klasik Modellerin Gelişen Teknolojilerle Bütünleştirilmesi. Springer Science & Business Media. s. 298. ISBN 978-0-387-40532-2.

- ^ Richard C. Dorf, 2018. Sensörler, Nanobilim, Biyomedikal Mühendisliği ve Aletler: Sensörler Nanobilim Biyomedikal Mühendisliği. CRC Basın. s. 4. ISBN 978-1-4200-0316-1.

- ^ David A. Patterson; John L. Hennessy, 2004. Bilgisayar Organizasyonu ve Tasarımı: Donanım / Yazılım Arayüzü, Üçüncü Baskı. Elsevier. s. 552. ISBN 978-0-08-050257-1.

- ^ "Sör Maurice Vincent Wilkes | İngiliz bilgisayar bilimcisi". Encyclopædia Britannica. Alındı 2016-12-11.

- ^ Berkeley, John L. Hennessy, Stanford Üniversitesi ve David A. Patterson, Kaliforniya Üniversitesi. "Bellek Hiyerarşisi Tasarımı - Bölüm 6. Intel Core i7, yanlışlıklar ve tuzaklar". EDN. Alındı 2016-12-11.

- ^ Shane Cook, 2012. CUDA Programlama: GPU'larla Paralel Hesaplamaya Yönelik Bir Geliştirici Kılavuzu. Newnes. s. 107–109. ISBN 978-0-12-415988-4.

- ^ Bruce Hellingsworth; Patrick Hall; Howard Anderson; 2001. Yüksek Ulusal Hesaplama. Routledge. s. 30–31. ISBN 978-0-7506-5230-8.

- ^ Reeta Sahoo, Gagan Sahoo. Infomatic Uygulamaları. Saraswati House Pvt Ltd. s. 1–. ISBN 978-93-5199-433-6.

- ^ Phillip A. Laplante; Seppo J. Ovaska; 2011. Gerçek Zamanlı Sistem Tasarımı ve Analizi: Uygulayıcı için Araçlar. John Wiley & Sons. s. 94–95. ISBN 978-1-118-13659-1.

- ^ a b c Hennessey ve Patterson. Bilgisayar Mimarisi: Nicel Bir Yaklaşım. Morgan Kaufmann. ISBN 9780123704900.

- ^ Çetin Kaya Koç, 2008. Kriptografi Mühendisliği. Springer Science & Business Media. sayfa 479–480. ISBN 978-0-387-71817-0.

- ^ David A. Patterson; John L. Hennessy; 2008. Bilgisayar Organizasyonu ve Tasarımı: Donanım / Yazılım Arayüzü. Morgan Kaufmann. sayfa 489–492. ISBN 978-0-08-092281-2.

- ^ Harvey G. Cragon, 2000. Bilgisayar Mimarisi ve Uygulaması. Cambridge University Press. s. 95–97. ISBN 978-0-521-65168-4.

- ^ Baker Mohammad, 2013. Çok Çekirdekli ve Yonga Üzerinde Sistemler için Gömülü Bellek Tasarımı. Springer Science & Business Media. sayfa 11–14. ISBN 978-1-4614-8881-1.

- ^ Gayde, William. "CPU'lar Nasıl Tasarlanır ve Oluşturulur". Techspot. Alındı 17 Ağustos 2019.

- ^ Vojin G. Oklobdzija, 2017. Dijital Tasarım ve İmalat. CRC Basın. s. 4. ISBN 978-0-8493-8604-6.

- ^ "Bellek Hiyerarşisi".

- ^ a b Solihin, Yan (2016). Paralel Çok Çekirdekli Mimarinin Temelleri. Chapman ve Hall. s. Bölüm 5: Bellek Hiyerarşisi Organizasyonuna Giriş. ISBN 9781482211184.

- ^ Yan Solihin, 2015. Paralel Çok Çekirdekli Mimarinin Temelleri. CRC Basın. s. 150. ISBN 978-1-4822-1119-1.

- ^ Steve Heath, 2002. Gömülü Sistem Tasarımı. Elsevier. s. 106. ISBN 978-0-08-047756-5.

- ^ Alan Clements, 2013. Bilgisayar Organizasyonu ve Mimarisi: Temalar ve Çeşitlemeler. Cengage Learning. s. 588. ISBN 1-285-41542-6.

- ^ a b c d e Solihin, Yan (2009). Paralel Bilgisayar Mimarisinin Temelleri. Solihin Yayıncılık. s. Bölüm 6: Bellek Hiyerarşisi Organizasyonuna Giriş. ISBN 9780984163007.

- ^ "Özel Önbellek Hiyerarşilerinin Performans Değerlendirmesi" (PDF).

- ^ David A. Patterson; John L. Hennessy; 2017. Bilgisayar Organizasyonu ve Tasarımı RISC-V Sürümü: Donanım Yazılım Arayüzü. Elsevier Science. s. 386–387. ISBN 978-0-12-812276-1.

- ^ Stefan Goedecker; Adolfy Hoisie; 2001. Sayısal Olarak Yoğun Kodların Performans Optimizasyonu. SIAM. s. 11. ISBN 978-0-89871-484-5.

- ^ Harvey G. Cragon, 1996. Bellek Sistemleri ve Ardışık Düzenlenmiş İşlemciler. Jones & Bartlett Öğrenimi. s. 47. ISBN 978-0-86720-474-2.

- ^ David A. Patterson; John L. Hennessy; 2007. Bilgisayar Organizasyonu ve Tasarımı, Gözden Geçirilmiş Baskı, Üçüncü Baskı: Donanım / Yazılım Arayüzü. Elsevier. s. 484. ISBN 978-0-08-055033-6.

- ^ "Paylaşımlı Önbellekli Çok Çekirdekli Sistemler için Yazılım Teknikleri". 2018-05-24.

- ^ "Çip Çoklu İşlemciler için Uyarlanabilir Paylaşılan / Özel NUCA Önbellek Bölümleme Şeması" (PDF). Arşivlenen orijinal (PDF) 2016-10-19 tarihinde.

- ^ Akanksha Jain; Calvin Lin; 2019. Önbellek Değiştirme Politikaları. Morgan & Claypool Yayıncıları. s. 45. ISBN 978-1-68173-577-1.

- ^ David Culler; Jaswinder Pal Singh; Anoop Gupta; 1999. Paralel Bilgisayar Mimarisi: Bir Donanım / Yazılım Yaklaşımı. Gulf Professional Publishing. s. 436. ISBN 978-1-55860-343-1.

- ^ a b Stephen W. Keckler; Kunle Olukotun; H. Peter Hofstee; 2009. Çok Çekirdekli İşlemciler ve Sistemler. Springer Science & Business Media. s. 182. ISBN 978-1-4419-0263-4.

- ^ a b "Intel Broadwell Mikromimarisi".

- ^ a b "Intel Kaby Lake Microrchitecture".

- ^ "Nehalem İşlemci ve Nehalem-EP SMP Platformlarının Mimarisi" (PDF). Arşivlenen orijinal (PDF) 2014-08-11 tarihinde.

- ^ "IBM Power7".