Direnç merdiveni - Resistor ladder

Bir direnç merdiveni tekrar eden birimlerden oluşan bir elektrik devresidir. dirençler. Aşağıda iki konfigürasyon ele alınmaktadır, bir dizi direnç merdiveni ve bir R – 2R merdiveni.

Bir R – 2R merdiveni, gerçekleştirmenin basit ve ucuz bir yoludur dijitalden analoğa dönüştürme, tekrarlayan hassas düzenlemeler kullanarak direnç ağları içinde merdiven benzeri yapılandırma. Bir dizi direnç merdiveni, tekrar etmeyen referans ağını uygular.

Dize direnci merdiven ağı (analogdan dijitale dönüştürme veya ADC)

İki referans gerilimi arasına bağlanan, genellikle eşit boyutta birçok dirençten oluşan bir dizi, bir direnç dizisi merdiven ağıdır. Dirençler şu şekilde hareket eder: gerilim bölücüler referans voltajlar arasında. Dizinin her bir dokunuşu, başka biriyle karşılaştırılabilecek farklı bir voltaj üretir. Voltaj: bu, bir flash ADC (analogtan dijitale dönüştürücü). Genellikle bir voltaj bir akım, bir R – 2R merdiven ağı kullanma olasılığını etkinleştirir.

- Dezavantaj: bir n-bit ADC, direnç sayısı katlanarak büyür, gibi dirençler gereklidir, R – 2R direnç merdiveni ise sadece ihtiyaç duyduğu için bit sayısıyla doğrusal olarak artar dirençler.

- Avantaj: Aynı sayıda bileşen kullanılarak daha yüksek empedans değerlerine ulaşılabilir.

R – 2R direnç merdiven ağı (dijitalden analoğa dönüştürme)

Şekil 1'de temel bir R – 2R direnç merdiven ağı gösterilmiştir. Bit an−1 (en önemli bit, MSB) bit a aracılığıyla0 (en az anlamlı bit, LSB) dijital mantık kapılarından sürülür. İdeal olarak, bit girişleri arasında geçiş yapılır V = 0 (mantık 0) ve V = Vref (mantık 1). R – 2R ağı, bu dijital bitlerin çıkış voltajına katkılarında ağırlıklandırılmasına neden olur Vdışarı. Hangi bitlerin 1'e ve hangilerinin 0'a ayarlandığına bağlı olarak, çıkış voltajı (Vdışarı) karşılık gelen kademeli değer 0 ile Vref eksi minimum adımın değeri, bit 0'a karşılık gelir. Vref (ve mantık 0'ın voltajı) dijital sinyalleri üretmek için kullanılan teknolojinin türüne bağlı olacaktır.[1]

Bir R – 2R DAC'nin dijital değeri VAL için N bit ve 0 V /Vref mantık seviyeleri, çıkış voltajı Vdışarı dır-dir:

Örneğin, eğer N = 5 (dolayısıyla 2N = 32) ve Vref = 3,3 V (tipik CMOS mantık 1 voltajı), sonra Vdışarı 0 volt arasında değişecektir (VAL = 0 = 000002) ve maksimum (VAL = 31 = 111112):

adımlarla (VAL = 1 = 00001'e karşılık gelir2)

R – 2R merdiveni ucuzdur ve üretimi nispeten kolaydır, çünkü yalnızca iki direnç değeri gereklidir (hatta bir, eğer R, bir çift 2R'yi paralel olarak yerleştirerek yapılırsa veya 2R, bir çift R yerleştirilerek yapılırsa dizi). Hızlıdır ve sabit çıkış empedansına sahiptir. R-2R merdiveni, bir dizi olarak çalışır. mevcut bölücüler, çıkış doğruluğu yalnızca her bir direncin diğerleriyle ne kadar iyi eşleştiğine bağlıdır. MSB dirençlerindeki küçük yanlışlıklar, LSB dirençlerinin katkısını tamamen etkileyebilir. Bu,monoton 01111 gibi büyük geçişlerde davranış2 10000'e kadar2. Kullanılan mantık kapılarının tipine ve mantık devrelerinin tasarımına bağlı olarak, mükemmel direnç değerlerinde bile bu tür büyük geçişlerde geçiş voltajı sıçramaları olabilir. Bunlar, çıkış düğümündeki kapasitans ile filtrelenebilir (bunun sonucunda bant genişliğindeki azalma bazı uygulamalarda önemli olabilir). Son olarak, 2R direnci dijital çıkış empedansı ile seri halindedir. Yüksek çıkış empedanslı kapılar (ör. LVDS ) bazı durumlarda uygun olmayabilir. Yukarıdaki nedenlerin tümü (ve şüphesiz diğerleri) için, bu tip DAC nispeten az sayıda bit ile sınırlı olma eğilimindedir; entegre devreler bit sayısını 14'e veya daha fazlasına itebilse de, 8 bit veya daha azı daha tipiktir.

R – 2R direnç merdivenlerinin doğruluğu

Daha önemli bitlerle kullanılan dirençler, daha az önemli bitlerle kullanılanlardan orantılı olarak daha doğru olmalıdır; örneğin, yukarıda tartışılan R – 2R ağında, bit-4 (MSB) dirençlerindeki yanlışlıklar R / 32'ye kıyasla önemsiz olmalıdır (yani,% 3'ten çok daha iyi). Dahası, 10000'de sorunları önlemek için2-to-011112 geçiş, alt bitlerdeki yanlışlıkların toplamı R / 32'den önemli ölçüde daha az olmalıdır. Gereken doğruluk her ek bit ile ikiye katlanır: 8 bit için gerekli doğruluk 1 / 256'dan (% 0,4) daha iyi olacaktır. İçinde Entegre devreler, yüksek doğruluklu R – 2R ağları kullanılarak doğrudan tek bir alt tabakaya yazdırılabilir ince tabaka teknoloji, dirençlerin benzer paylaşmasını sağlamak elektriksel özellikleri. Öyle olsa bile, genellikle lazerle kesilmiş gerekli hassasiyeti elde etmek için. Böyle çip üzerinde direnç merdivenleri dijitalden analoğa dönüştürücüler 16-bit doğruluğa ulaşıldığı gösterilmiştir.[2] Bir baskılı devre kartında, ayrı bileşenler kullanarak,% 1 doğrulukta dirençler 5 bitlik bir devre için yeterli olacaktır, ancak bunun ötesinde bit sayıları ile giderek artan hassas dirençlerin maliyeti engelleyici hale gelir. 10 bitlik bir dönüştürücü için,% 0,1'lik hassas dirençler kullanmak bile çıktının monotonluğunu garanti etmez. Bu, bazen, ayrık bileşenlerden oluşturulan yüksek çözünürlüklü R-2R merdivenleri kullanılır, doğrusal olmama yazılımda düzeltilir. Böyle bir yaklaşımın bir örneği Korad 3005 güç kaynağında görülebilir.

Eşit olmayan basamaklara sahip direnç merdiveni

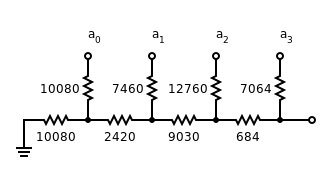

R – 2R merdiveninin her "basamağının" aynı direnç değerlerini kullanması gerekli değildir. Yalnızca "2R" değerinin "R" değerinin toplamı ile eşleşmesi gerekir. Thévenin eşdeğeri düşük anlamlı basamakların direnci. Şekil 2, eşit olmayan dirençlere sahip doğrusal bir 4-bit DAC'yi göstermektedir.

Bu, DAC'yi her seferinde bir bit oluşturarak heterojen bir direnç koleksiyonundan makul derecede doğru bir DAC oluşturulmasına izin verir. Her aşamada, "basamak" ve "bacak" için dirençler, basamak değeri bacak değeri artı önceki basamakların eşdeğer direnci ile eşleşecek şekilde seçilir. Basamak ve bacak dirençleri, mevcut kombinasyonların sayısını artırmak için diğer dirençleri seri veya paralel olarak eşleştirerek oluşturulabilir. Bu süreç otomatikleştirilebilir.

Ayrıca bakınız

Referanslar

Dış bağlantılar

- ECE209: DAC Ders Notları - Ohio Devlet Üniversitesi

- EE247: D / A Dönüştürücüler - Berkeley University of California

- Basitleştirilmiş DAC / ADC Ders Notları - Michigan üniversitesi

- Dijital - Analog Dönüştürücüler (slaytlar) - Georgia Tech

- Eğitim MT-014: Dize DAC'leri ve Tamamen Çözülmüş DAC'ler - Analog cihazlar

- Eğitim MT-015: İkili DAC'ler - Analog cihazlar

- Öğretici MT-016: Bölümlenmiş DAC'ler - Analog cihazlar

- Eğitim MT-018: Kasıtlı Olarak Doğrusal Olmayan DAC'ler - Analog cihazlar

- R2R Direnç Merdiveni Ağları - BI Teknolojileri

- R / 2R Ladder Networks Uygulama Notu - TT Elektronik