Klasik RISC ardışık düzeni - Classic RISC pipeline

Bu makale şunları içerir: referans listesi, ilgili okuma veya Dış bağlantılar, ancak kaynakları belirsizliğini koruyor çünkü eksik satır içi alıntılar. (Aralık 2012) (Bu şablon mesajını nasıl ve ne zaman kaldıracağınızı öğrenin) |

İçinde bilgisayar donanımı tarihi biraz erken indirgenmiş komut seti bilgisayarı merkezi işlem birimleri (RISC CPU'lar) çok benzer bir mimari çözüm kullandı, şimdi bir klasik RISC ardışık düzeni. Bu CPU'lar şunlardı: MIPS, SPARC, Motorola 88000 ve daha sonra kavramsal CPU DLX eğitim için icat edildi.

Bu klasik skaler RISC tasarımlarının her biri alır ve yürütmeye çalışır. döngü başına bir talimat. Her tasarımın ana ortak konsepti beş aşamalı bir uygulamadır. talimat boru hattı. Operasyon sırasında, her bir boru hattı aşaması bir seferde bir talimat üzerinde çalışır. Bu aşamaların her biri bir dizi parmak arası terlik devleti tutmak ve kombinasyonel mantık bu flip-flopların çıktıları üzerinde çalışır.

Klasik beş aşamalı RISC ardışık düzeni

Talimat getirme

Talimatlar, okunması bir döngü süren bellekte bulunur. Bu bellek ayrılmış SRAM veya bir Yönerge olabilir Önbellek. "Gecikme" terimi bilgisayar bilimlerinde sıklıkla kullanılır ve bir işlemin başladığı andan tamamlanana kadar geçen süre anlamına gelir. Böylece, talimat getirme bir gecikme süresine sahiptir. saat döngüsü (tek döngülü SRAM kullanılıyorsa veya talimat önbellekteyse). Böylece, Talimat Getirme aşama, komut belleğinden 32 bitlik bir talimat alınır.

Program sayıcı veya PC, talimat belleğine sunulan adresi tutan bir kayıttır. Bir döngünün başlangıcında, adres talimat belleğine sunulur. Daha sonra döngü sırasında komut, talimat belleğinden okunur ve aynı zamanda bir sonraki PC'yi belirlemek için bir hesaplama yapılır. Bir sonraki PC'nin hesaplanması, PC'yi 4 artırarak ve bunu bir sonraki PC olarak mı alacağınızı yoksa alternatif olarak bir dallanma / atlama hesaplamasının sonucunu bir sonraki PC olarak mı alacağınızı seçerek yapılır. Klasik RISC'de tüm talimatların aynı uzunluğa sahip olduğunu unutmayın. (Bu, RISC'yi CISC'den ayıran bir şeydir. [1]). Orijinal RISC tasarımlarında, bir komutun boyutu 4 bayttır, bu nedenle komut adresine her zaman 4 ekleyin, ancak alınan dallanma, atlama veya istisna durumunda PC + 4 kullanmayın (bkz. gecikmiş şubeler, altında). (Bazı modern makinelerin daha karmaşık algoritmalar kullandığını unutmayın (şube tahmini ve şube hedefi tahmini ) sonraki talimat adresini tahmin etmek için.)

Talimat kod çözme

İlk RISC makinelerini önceki CISC makinelerinden ayıran başka bir şey de, RISC'nin mikro kod.[2] CISC mikro kodlu talimatlar durumunda, talimat önbelleğinden getirildikten sonra komut bitleri, her bir boru hattı aşamasındaki basit kombinasyon mantığının doğrudan komut bitlerinden veri yolu için kontrol sinyalleri ürettiği boru hattında aşağı kaydırılır. Bu CISC tasarımlarında, geleneksel olarak kod çözme aşaması olarak adlandırılan aşamada çok az kod çözme yapılır. Bu kod çözme eksikliğinin bir sonucu, talimatın ne yaptığını belirtmek için daha fazla komut bitinin kullanılması gerekmesidir. Bu, indeks kaydı gibi şeyler için daha az bit bırakır.

Tüm MIPS, SPARC ve DLX komutları en fazla iki kayıt girişine sahiptir. Kod çözme aşamasında, bu iki kaydın indeksleri komut içinde tanımlanır ve indeksler adres olarak kayıt hafızasına sunulur. Böylece, adı geçen iki kayıt, kayıt dosyası. MIPS tasarımında, kayıt dosyası 32 girdiye sahipti.

Aynı zamanda kayıt dosyası okunur, bu aşamadaki komut verme mantığı, boru hattının bu aşamadaki talimatı yürütmeye hazır olup olmadığını belirler. Değilse, sorun mantığı hem Talimat Getirme aşamasının hem de Kod Çözme aşamasının durmasına neden olur. Bir durma döngüsünde, giriş flip flopları yeni bitleri kabul etmez, bu nedenle bu döngü sırasında yeni hesaplamalar yapılmaz.

Kodu çözülen talimat bir dallanma veya atlama ise, dallanma veya atlamanın hedef adresi, kayıt dosyasının okunmasıyla paralel olarak hesaplanır. Dallanma koşulu, aşağıdaki döngüde hesaplanır (kayıt dosyası okunduktan sonra) ve dallanma alınırsa veya komut bir atlama ise, ilk aşamadaki PC'ye dallanma hedefi atanır. hesaplandı. Bazı mimariler, Aritmetik mantık Birimi (ALU), biraz azaltılmış talimat verimi pahasına Yürütme aşamasında.

Kod çözme aşaması, oldukça fazla donanımla sonuçlandı: MIPS, iki yazmaç eşitse dallanma olasılığına sahiptir, bu nedenle, kayıt dosyası okunduktan sonra 32 bit genişliğinde bir AND ağacı seri halinde çalışır, bu da çok uzun bir kritik yol oluşturur. aşama (bu, saniyede daha az döngü anlamına gelir). Ayrıca, dal hedefi hesaplaması genellikle 16 bitlik bir ekleme ve 14 bitlik bir artırıcı gerektirdi. Dalın kod çözme aşamasında çözülmesi, yalnızca tek döngülü bir dal yanlış tahmin cezasına sahip olmayı mümkün kıldı. Dallar çok sık alındığı (ve dolayısıyla yanlış tahmin edildiği) için bu cezayı düşük tutmak çok önemliydi.

Yürüt

Yürütme aşaması, gerçek hesaplamanın gerçekleştiği yerdir. Tipik olarak bu aşama bir ALU ve biraz değiştiriciden oluşur. Aynı zamanda bir çoklu döngü çarpanı ve bölücü içerebilir.

ALU, boole işlemlerini gerçekleştirmekten (ve veya değil, nand, nor, xor, xnor) ve ayrıca tamsayı toplama ve çıkarma işlemlerinden sorumludur. Sonucun yanı sıra, ALU tipik olarak sonucun 0 olup olmadığı veya bir taşma olup olmadığı gibi durum bitleri sağlar.

Bit değiştirici, kaydırma ve rotasyonlardan sorumludur.

Bu basit RISC makineleriyle ilgili talimatlar, işlemin türüne göre üç gecikme sınıfına ayrılabilir:

- Kayıt-Kayıt İşlemi (Tek döngü gecikme): Ekleme, çıkarma, karşılaştırma ve mantıksal işlemler. Yürütme aşamasında, iki argüman, yürütme aşamasının sonunda sonucu oluşturan basit bir ALU'ya beslendi.

- Bellek Referansı (İki döngülü gecikme). Tüm yükler bellekten. Yürütme aşamasında, ALU, döngünün sonunda sanal bir adres üretmek için iki argüman (bir kayıt ve bir sabit ofset) ekledi.

- Çok döngülü Talimatlar (Birçok döngü gecikmesi). Tamsayı çarpma ve bölme ve tümü kayan nokta operasyonlar. Yürütme aşamasında, bu işlemlerin işlenenleri çok döngülü çoğaltma / bölme birimine beslendi. Çoğaltma / bölme birimi işini yaparken, boru hattının geri kalanı yürütmeye devam etmekte özgürdü. Geri yazma aşamasını ve sorun mantığını karmaşıklaştırmaktan kaçınmak için, çok döngülü talimat sonuçlarını ayrı bir kayıt kümesine yazdı.

Bellek erişimi

Veri belleğine erişilmesi gerekiyorsa, bu aşamada yapılır.

Bu aşamada, tek döngülü gecikme talimatlarının sonuçları bir sonraki aşamaya iletilir. Bu yönlendirme, hem bir hem de iki döngü komutunun sonuçlarını her zaman boru hattının aynı aşamasında yazmasını sağlar, böylece kayıt dosyasına sadece bir yazma portu kullanılabilir ve her zaman kullanılabilir.

Doğrudan eşlenmiş ve sanal olarak etiketlenmiş veri önbelleğe alma için, açık ara en basit olanı çok sayıda veri önbellek organizasyonu, iki SRAM'ler biri veri depolamak ve diğeri etiketleri depolamak için kullanılır.

Cevap yazmak

Bu aşamada, hem tek döngü hem de iki döngü komutu sonuçlarını kayıt dosyasına yazar.İki farklı aşamanın kayıt dosyasına aynı anda eriştiğini unutmayın - kod çözme aşaması, aynı anda iki kaynak kaydını okur. geri yazma aşaması, önceki bir talimatın hedef kaydını yazmaktır. Gerçek silikonda bu bir tehlike olabilir (tehlikeler hakkında daha fazla bilgi için aşağıya bakın). Bunun nedeni, kod çözmede okunan kaynak yazmaçlarından birinin geri yazma işleminde yazılan hedef yazmaç ile aynı olabilmesidir. Bu olduğunda, yazmaç dosyasındaki aynı bellek hücreleri aynı anda hem okunur hem de yazılır. Silikonda, bellek hücrelerinin birçok uygulaması aynı anda okunduğunda ve yazıldığında doğru çalışmayacaktır.

Tehlikeler

Hennessy ve Patterson terimi icat etti tehlike bir boru hattındaki talimatların yanlış cevaplar üreteceği durumlar için.

Yapısal tehlikeler

Yapısal tehlikeler, iki talimatın aynı kaynakları aynı anda kullanmaya çalıştığı durumlarda ortaya çıkar. Klasik RISC ardışık düzenleri, donanımı kopyalayarak bu tehlikelerden kaçındı. Özellikle, şube talimatları, dalın hedef adresini hesaplamak için ALU'yu kullanabilirdi. ALU bu amaç için kod çözme aşamasında kullanılmış olsaydı, bir ALU talimatı ve onu takip eden bir dal, her iki talimatın da ALU'yu aynı anda kullanmaya çalıştığını görürdü. Kod çözme aşamasına özel bir dal hedef toplayıcı tasarlayarak bu çatışmayı çözmek basittir.

Veri tehlikeleri

Körü körüne programlanan bir talimat, veriler kayıt dosyasında mevcut olmadan önce verileri kullanmaya çalıştığında veri tehlikeleri ortaya çıkar.

Klasik RISC ardışık düzeninde, Veri tehlikelerinden iki yoldan biriyle kaçınılır:

Çözüm A. Baypas

Baypas etme aynı zamanda işlenen yönlendirme.

CPU'nun aşağıdaki kod parçasını çalıştırdığını varsayalım:

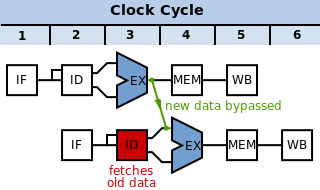

ALT r3,r4 -> r10 ; R3 - r4 ila r10'u yazarVE r10,r3 -> r11 ; R10 ve r3'ü r11'e yazarKomut getirme ve kod çözme aşamaları, ikinci talimatı ilkinden bir döngü sonra gönderir. Bu şemada gösterildiği gibi boru hattından aşağı akarlar:

İçinde saf boru hattı, tehlike dikkate alınmadan, veri tehlikesi aşağıdaki şekilde ilerler:

3. döngüde, ALT talimat için yeni değeri hesaplar r10. Aynı döngüde VE işlemin kodu çözülür ve değeri r10 kayıt dosyasından alınır. Ancak ALT talimat henüz sonucunu yazmadı r10. Bunun geri yazımı normalde 5. döngüde (yeşil kutu) gerçekleşir. Bu nedenle, kayıt dosyasından okunan ve ALU'ya geçen değer (uygulamanın Yürütme aşamasında) VE kırmızı kutu) yanlıştır.

Bunun yerine, hesaplanan verileri aktarmalıyız ALT Yürütme aşamasına (yani diyagramdaki kırmızı daireye) geri dönün. VE operasyon önce normalde geri yazılır. Bu sorunun çözümü bir çift baypas çoklayıcıdır. Bu çoklayıcılar, kod çözme aşamasının sonunda yer alır ve başarısız olan çıkışları, ALU'nun girdileridir. Her çoklayıcı aşağıdakiler arasından seçim yapar:

- Bir kayıt dosyası okuma portu (yani, saf boru hattında olduğu gibi kod çözme aşamasının çıktısı): kırmızı ok

- ALU'nun mevcut kayıt boru hattı (bir aşamayı atlamak için): mavi ok

- Erişim aşamasının mevcut kayıt boru hattı (yüklü bir değer veya iletilen bir ALU sonucudur, bu iki aşamayı atlamayı sağlar): mor ok. Bunun, verilerin aktarılmasını gerektirdiğini unutmayın geriye doğru zaman içinde bir döngü. Bu olursa, bir kabarcık durdurmak için takılmalıdır

VEveriler hazır olana kadar işlem.

Kod çözme aşaması mantığı, boru hattının yürütme ve erişim aşamalarındaki talimatlarla yazılan kayıtları, kod çözme aşamasındaki talimatla okunan yazmaçlarla karşılaştırır ve çoklayıcıların en yeni verileri seçmesine neden olur. Bu baypas çoklayıcıları, boru hattının sadece ALU, çoklayıcı ve bir flip-flop'un gecikmesiyle basit komutları yürütmesini mümkün kılar. Çoklayıcılar olmadan, yazmaç dosyasını yazma ve sonra okuma gecikmesi bu talimatların gecikmesine dahil edilmelidir.

Verilerin yalnızca aktarılabileceğini unutmayın ileri zamanında - veriler henüz işlenmemişse daha önceki bir aşamaya atlanamaz. Yukarıdaki durumda, veriler ileri iletilir ( VE ALU'daki kayıt için hazırsa, ALT zaten hesapladı).

Çözüm B. Boru hattı kilidi

Ancak aşağıdaki talimatları göz önünde bulundurun:

LD adr -> r10VE r10,r3 -> r11Adresten okunan veriler adr veri önbelleğinde, ürünün Bellek Erişimi aşamasına kadar mevcut değildir. LD talimat. Bu zamana kadar VE talimat zaten ALU üzerinden. Bunu çözmek için bellekteki verilerin ALU girişine zaman içinde geriye doğru aktarılması gerekir. Bu mümkün değil. Çözüm, geciktirmektir. VE bir döngü ile talimat. Veri tehlikesi kod çözme aşamasında tespit edilir ve getirme ve kod çözme aşamaları durdu - girişlerini düşürmeleri engellenir ve bu nedenle bir döngü boyunca aynı durumda kalırlar. Aşağı akıştaki yürütme, erişim ve geri yazma aşamaları, arasına eklenen ekstra bir işlemsiz talimatını (NOP) görür. LD ve VE Talimatlar.

Bu NOP bir ardışık düzen olarak adlandırılır kabarcık çünkü boru hattında bir hava kabarcığı gibi yüzer, kaynakları işgal eder, ancak faydalı sonuçlar üretmez. Bir veri tehlikesini tespit eden ve tehlike ortadan kalkıncaya kadar boru hattını durduran donanıma, boru hattı kilidi.

| Zamanda geriye gitme | Balon kullanılarak çözülen sorun |

|  |

Bununla birlikte, bir ardışık düzen kilidinin herhangi bir veri iletimi ile kullanılması gerekmez. İlk örnek ALT bunu takiben VE ve ikinci örnek LD bunu takiben VE İlk aşamayı, geri yazma elde edilene kadar üç döngü geciktirerek çözülebilir ve kayıt dosyasındaki veriler doğrudur, bu da doğru kayıt değerinin bilgisayar tarafından alınmasına neden olur. VEKod Çözme aşaması. İşlemci hiçbir şeyi işlemeden çok fazla zaman harcadığından, bu oldukça performans düşüşüne neden olur, ancak beklemek için daha az yönlendirme mantığı olduğundan saat hızları artırılabilir.

Bu veri tehlikesi, programın makine kodu derleyici tarafından yazıldığında oldukça kolay bir şekilde tespit edilebilir. Stanford MIPS makine, ilk iki boru hattı aşamasını algılamak ve (daha fazla masraflı bir şekilde) geciktirmek için devrelere sahip olmak yerine, bu durumda NOP talimatlarını eklemek için derleyiciye güvendi. Bu nedenle MIPS adı: Birbirine Bağlı Ardışık Düzen Aşamaları Olmayan Mikroişlemci. Derleyici tarafından eklenen ekstra NOP komutlarının, program ikililerini, talimat önbelleği isabet oranının düşürülmesine yetecek kadar genişlettiği ortaya çıktı. Stall donanımı pahalı olmasına rağmen, talimat önbelleği isabet oranını iyileştirmek için daha sonraki tasarımlara geri getirildi, bu noktada kısaltma artık mantıklı değildi.

Kontrol tehlikeleri

Kontrol tehlikeleri, koşullu ve koşulsuz dallanmadan kaynaklanır. Klasik RISC ardışık düzeni dalları kod çözme aşamasında çözer, bu da dal çözümleme yinelemesinin iki döngü uzunluğunda olduğu anlamına gelir. Bunun üç sonucu vardır:

- Dal çözümlemesi yinelemesi epey bir devreden geçer: talimat önbelleği okuma, kayıt dosyası okuma, dal durumu hesaplama (MIPS CPU'larında 32 bitlik bir karşılaştırma içerir) ve sonraki komut adresi çoklayıcı.

- Dallanma ve atlama hedefleri yazmaç okumasına paralel olarak hesaplandığından, RISC ISA'ları tipik olarak bir yazmaç + ofset adresine dallanan talimatlara sahip değildir. Kaydolmak için atlama desteklenmektedir.

- Alınan herhangi bir dalda, daldan hemen sonraki talimat her zaman talimat önbelleğinden alınır. Bu talimat göz ardı edilirse, alınan dal başına bir döngü vardır IPC yeterince büyük olan ceza.

Bu performans sorununu şubelerle çözmek için dört şema vardır:

- Tahmin Alınmadı: Talimatı daldan sonra daima talimat önbelleğinden alın, ancak sadece dal alınmazsa çalıştırın. Dal alınmazsa, boru hattı dolu kalır. Dal alınırsa, talimat temizlenir (bir NOPmuş gibi işaretlenir) ve bir döngünün bir talimatı bitirme fırsatı kaybedilir.

- Dallanma Olasılığı: Her zaman daldan sonra talimatı komut önbelleğinden alın, ancak bunu yalnızca dal alınmışsa çalıştırın. Derleyici, böyle bir daldaki dal gecikme aralığını her zaman doldurabilir ve dallar daha sık alındığından, bu tür dalların önceki türden daha küçük bir IPC cezası vardır.

- Dal Gecikme Yuvası: Her zaman daldan sonra talimatı komut önbelleğinden getir ve dal alınmış olsa bile her zaman yürüt. Alınan (belki% 60) veya alınmayan (belki% 40) dalların bir kısmı için IPC cezası almak yerine, dallanma gecikmesi yuvaları, derleyicinin dallanma gecikmesi aralığını programlayamadığı dallar için IPC cezası alır. SPARC, MIPS ve MC88K tasarımcıları, ISA'larına bir şube gecikme yuvası tasarladılar.

- Şube Tahmin: Her komutu getirmeye paralel olarak, komutun dallanma mı yoksa atlama mı olduğunu tahmin edin ve öyleyse hedefi tahmin edin. Dal veya atlamadan sonraki döngüde, talimatı tahmin edilen hedefe getirin. Tahmin yanlış olduğunda, yanlış getirilen hedefi temizleyin.

Gecikmiş dallar tartışmalıydı, çünkü anlamsallıkları karmaşıktı. Geciken dal, yeni bir konuma atlamanın gerçekleştiğini belirtir sonra sonraki talimat. Bir sonraki talimat, daldan sonra talimat önbelleği tarafından kaçınılmaz olarak yüklenen komuttur.

Geciken şubeler eleştirildi[Kim tarafından? ] ISA tasarımında zayıf bir kısa vadeli seçim olarak:

- Derleyiciler tipik olarak daldan sonra yerleştirilecek mantıksal olarak bağımsız talimatlar bulmakta güçlük çekerler (daldan sonraki talimat, gecikme yuvası olarak adlandırılır), böylece NOP'leri gecikme yuvalarına eklemeleri gerekir.

- Süper skalar Döngü başına birden çok talimat getiren ve bir tür dal tahminine sahip olması gereken işlemciler, gecikmiş dallardan yararlanmaz. Alfa ISA, süper skalar işlemciler için tasarlandığı için gecikmiş şubeleri dışarıda bıraktı.

- Gecikmiş şubelerin en ciddi dezavantajı, içerdikleri ek kontrol karmaşıklığıdır. Gecikme yuvası talimatı bir istisna alırsa, işlemcinin bir sonraki talimat yerine dalda yeniden başlatılması gerekir. O zaman istisnaların esasen iki adresi vardır, istisna adresi ve yeniden başlatma adresi ve her durumda ikisi arasında doğru bir şekilde oluşturmak ve ayırt etmek, sonraki tasarımlar için bir hata kaynağı olmuştur.

İstisnalar

32 bitlik bir RISC'nin iki büyük sayı ekleyen bir ADD komutunu işlediğini ve sonucun 32 bite sığmadığını varsayalım. Ne oluyor?

Çoğu mimarinin sağladığı en basit çözüm, aritmetiği sarmalamaktır. Olası maksimum kodlanmış değerden daha büyük sayıların en önemli bitleri, sığana kadar kesilir. Normal tam sayı sisteminde, 3000000000 + 3000000000 = 6000000000. İşaretsiz 32 bit sarma aritmetiği ile, 3000000000 + 3000000000 = 1705032704 (6000000000 mod 2 ^ 32). Bu çok kullanışlı görünmeyebilir. Aritmetiğe sarmanın en büyük yararı, her işlemin iyi tanımlanmış bir sonuca sahip olmasıdır.

Ancak programcı, özellikle destekleyen bir dilde programlama yapıyorsa büyük tamsayılar (Örneğin. Lisp veya Şema ), aritmetik sarma istemeyebilir. Bazı mimariler (ör. MIPS), sonucu sarmak yerine taşma durumunda özel konumlara ayrılan özel ekleme işlemleri tanımlar. Sorunun çözülmesinden hedef konumdaki yazılım sorumludur. Bu özel şubeye istisna denir. İstisnalar, hedef adresin talimatın kendisi tarafından belirtilmemesi ve şube kararının talimatın sonucuna bağlı olması nedeniyle normal şubelerden farklılık gösterir.

Klasik RISC makinelerinden birindeki en yaygın yazılım tarafından görülebilen istisna türü, TLB eksik.

İstisnalar, dallar ve atlamalardan farklıdır çünkü diğer kontrol akışı değişiklikleri kod çözme aşamasında çözülür. Geri yazma aşamasında istisnalar çözülür. Bir istisna tespit edildiğinde, aşağıdaki talimatlar (boru hattının başlarında) geçersiz olarak işaretlenir ve borunun sonuna kadar akarken sonuçları atılır. Program sayacı, özel bir istisna işleyicisinin adresine ayarlanır ve özel kayıtlar istisna konumu ve nedeni ile yazılır.

Yazılımın sorunu çözmesini ve programı yeniden başlatmasını kolaylaştırmak (ve hızlı) için CPU'nun kesin bir istisna yapması gerekir. Kesin bir istisna, istisnai talimata kadar olan tüm komutların yürütüldüğü ve istisnai talimatın ve sonrasındaki her şeyin yürütülmediği anlamına gelir.

Kesin istisnalar almak için, CPU'nun işlemek program sırasında yazılımın görünür durumundaki değişiklikler. Bu sıralı taahhüt, klasik RISC ardışık düzeninde çok doğal bir şekilde gerçekleşir. Çoğu talimat, sonuçlarını geri yazma aşamasında kayıt dosyasına yazar ve bu nedenle bu yazmalar otomatik olarak program sırasına göre gerçekleşir. Bununla birlikte, depolama talimatları sonuçlarını erişim aşamasında Veri Saklama Kuyruğuna yazarlar. Depo talimatı bir istisna alırsa, Depo Veri Kuyruğu girişi, daha sonra önbellek verisi SRAM'a yazılmaması için geçersiz kılınır.

Önbellek eksik işleme

Bazen, veri veya talimat önbelleği gerekli bir veri veya talimat içermez. Bu durumlarda, CPU, önbellek gerekli verilerle doldurulana kadar işlemi askıya almalı ve ardından yürütmeye devam etmelidir. Önbelleği gerekli verilerle doldurma (ve muhtemelen boşaltılan önbellek hattını belleğe geri yazma) sorunu, işlem hattı organizasyonuna özgü değildir ve burada tartışılmamaktadır.

Askıya alma / devam ettirme sorununu çözmek için iki strateji vardır. Birincisi, küresel bir durma sinyalidir. Bu sinyal, etkinleştirildiğinde, genellikle her aşamanın başlangıcında saati parmak arası terliklerle sınırlayarak, talimatların boru hattında ilerlemesini önler. Bu stratejinin dezavantajı, çok sayıda flip flop olmasıdır, bu nedenle global stall sinyalinin yayılması uzun zaman alır. Makine genellikle durmayı gerektiren koşulu belirlediği aynı döngüde durmak zorunda kaldığından, durma sinyali hız sınırlayıcı bir kritik yol haline gelir.

Askıya alma / sürdürme işleminin üstesinden gelmek için başka bir strateji, istisna mantığını yeniden kullanmaktır. Makine sorun teşkil eden talimatta bir istisna yapar ve diğer tüm talimatlar geçersiz kılınır. Önbellek gerekli verilerle doldurulduğunda, önbelleğin ıskalanmasına neden olan talimat yeniden başlar. Veri önbelleği eksik işlemeyi hızlandırmak için, erişim döngüsü veri önbelleği doldurulduktan bir döngü sonra gerçekleşecek şekilde talimat yeniden başlatılabilir.

Referanslar

- Hennessy, John L .; Patterson, David A. (2011). Bilgisayar Mimarisi, Nicel Bir Yaklaşım (5. baskı). Morgan Kaufmann. ISBN 978-0123838728.

- ^ Patterson, David. "RISC I: Azaltılmış Komut Seti VLSI Bilgisayarı". Alıntı dergisi gerektirir

| günlük =(Yardım) - ^ Patterson, David. "RISC I: Azaltılmış Komut Seti VLSI Bilgisayarı". Alıntı dergisi gerektirir

| günlük =(Yardım)